Number of hours

- Lectures 12.0

- Projects 30.0

- Tutorials -

- Internship -

- Laboratory works -

- Written tests -

ECTS

ECTS 2.5

Goal(s)

At the end of the course, the students will be able to specify analog and digital system architectures in order to outsource design and manufacturing of integrated systems

Specific objectives

- Microelectronics trends and physical limitations

- ASIC architecture exploration, specification, design and verification flows

- ASIC technologies

Responsible(s)

Vincent BEROULLE

Content(s)

- Introduction to microelectronic

- Context, trends and issues

- ASIC design flow

- Microelectronic principal actors

- ASIC technologies (pre-diffused, pre-characterized, full custom)

- Logic gate design in CMOS pre-characterized technology

- Transistor level schematic of CMOS digital gates

- Delay and metastability

- CMOS ASIC fabrication (photolithography)

- CMOS layout design

- TOP-DOWN design flow

- Principles of analog and mixed simulation

- Analog and mixed simulation

- VHDL-AMS language bases

- VHDL-AMS standard

- VHDL-AMS general writing

- VHDL-AMS new objects

- Simultaneous instructions

- Language attribute and kernel synchronization

- Solvability criterion

Laboratories

Architecture system exploration using VHDL-AMS language

Programmable components (FPGA, CPLD), logical synthesis (VHDL or verilog front-end design flow), electrical characteristics of MOS transistors (nMOS, pMOS), Analog simulation tools (Spice), sensor instumentation, C for embedded systems

Test

- E1 = final written exam (session 1), , written, 1h30, only allowed document "Syntaxe VHDL-AMS", no calculator

- P = project (no second session)

- E2 = final written exam (session 1), , written, 1h30, only allowed document "Syntaxe VHDL-AMS", no calculator

Calendar

The course exists in the following branches:

- Curriculum - EIS - Semester 7

Additional Information

Course ID : 4AMEE410

Course language(s):

The course is attached to the following structures:

You can find this course among all other courses.

Bibliography

- CMOS VLSI Design, A circuit and Systems Perspective, 3ème édition, N. Weste, D. Harris, Addison Wesley

- Digital Digital of Integrated Circuits: A Design Perspective by Jan M. Rabaey, Prentice Hall; ISBN: 013178609

- VHDL-AMS : Applications et enjeux industriels » de Y. Hervé

- The system designer’s guide to VHDL-AMS, de P.J. Ashenden et all.,Elsevier science

- The designer’s guide to Verilog AMS de K.S. Kundert et all., Kluwer

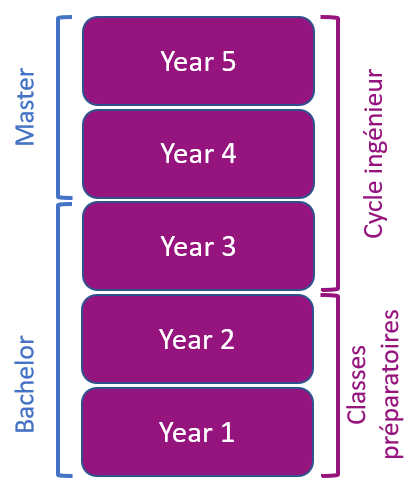

What is a grande école ?

French engineering curriculum