Number of hours

- Lectures 24.0

- Tutorials 12.0

- Laboratory works 18.0

ECTS

ECTS 6.0

Goal(s)

At the end of the lecture, the students will be able to verify, to test digital architectures and to analyse the vulnerabilities of embedded systemes. Then, they will be able to perform attacks and to design appropriate countermeasures.

Contact David HELY, Vincent BEROULLE

David HELY, Vincent BEROULLE

Content(s)

- Verification and test of digital systems

- Introduction

- Context and issues

- Verification vs Test

- DO-254 Standard

- Harwdware systems verification

- Simulation

- Emulation & Prototyping

- Hardware Testing

- Defects and faults modeling

- Automatic Test Pattern Generation (ATPG)

- Design for Test and Bult-in-Self-Test (DfT, BIST)

- Digital board testing (boundary scan)

- Introduction

- HW/SW Verification

- Microelectronic context and trends (SoC, MPSOC)

- SoC design flow

- Hardware/Software Co-design approach

- Plateform based design

- Introduction to SystemC

- Starting with SystemC

- Communication channels (Fifo, Mutex, Semaphore)

- New abstraction level : Transaction Level Modeling (TLM)

- Co-verification of Hardware and Software systems

- Context et definitions

- Co-verification approaches based on ISS, BFM, TLM, and emulation

- Criteria to choose a verification approach

- Hardware Security

##Introduction

##Cryptography basis- Hardware Vulnerabilities

- Fault Attacks

- Side Chanel Attacks

- Integrated Circuit Trustworthiness

##Countermeasures

##Security Certification

##Case studies - Smartcard

- FPGA

- Hardware Vulnerabilities

Laboratories

- TP1 : VHDL & PSL Simulation with QuestaSim (Mentor GraphiCs)

- TP2 : Simulation vs "prototyping and integrated logical analyzer" ChipScopePro (Xilinx)

- TP3 : SRAM embedded memory test on FPGA Spartan 3 card (Xilinx)

- TP1 : On the use of communication channels (Fifo, Mutex, Semaphore) to model a communication architecture

- TP2 : SoCLib - "Emulation of a Hardware/Software architecture used for image processing"

Prerequisites

Neccessary: Hardware Description Language (HDL, verilog or VHDL) for simulation (testbench) and design, logical synthesis, FPGA, processor architecture (processor models, instruction set architecture), C programming

Ideally: bases of object oriented programming

E1 = Terminal Exam, First session, written, 3h, only document allowed "syntaxe VHDL", no calculator

TP = average of laboratory exams

E2 = Exam, Second session, written 3h, only document allowed "syntaxe VHDL", no calculator

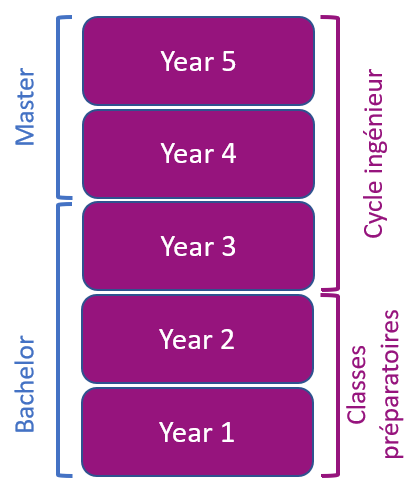

The course exists in the following branches:

- Curriculum - - Semester 5

- Curriculum - EIS - Semester 5

- Curriculum - EIS (Apprenticeship) - Semester 5

- Writing testbenches – functional verification of HDL models, Kluwer, Janick Bergeron

- Comprehensive functional verification, Bruce Wile, Elsevier, 2005

- A practical introduction to PSL, Cindy Eisner, Dana Fisman, Springer

- Security and Embedded Systems, Vol. 2 by Dimitrios Nikilaou Serpanos (Editor), Ran Giladi, R. Giladi (Editor)

French State controlled diploma conferring a Master's degree

What is a grande école ?

French engineering curriculum