Informations générales

Number of hours

- Lectures 3.0

- Projects 12.0

- Tutorials ?

- Internship ?

- Laboratory works 12.0

- Written tests ?

ECTSECTS

3.0

Goal(s)

To be able to choose and to exploit the more appropriate processor architecture for a given application

To be familliar with SOC design techniques and challenges

Contact David HELY

Responsible(s)

David HELY

Content(s)

- Introduction

- System vs Embedded Systems

- SOC design challenges

- SOC Modelling

- Hardware Software partitionning

- System on programmable chip Architectures

- SOPC design flow

- Applications

Prerequisites

*Digital design

-

- VHDL or Verilog

- FPGA design

- Embedded software Programming

**C

**Assembly Language - Processor Architecture

**RISC Architecture

**ARM processor

Test

Semester 5 - The exam is given in english only

Exam 1h30

Labs

Calendar

The course exists in the following branches:

- Curriculum - - Semester 5

- Curriculum - EIS - Semester 5

- Curriculum - EIS (Apprenticeship) - Semester 5

Additional Information

Curriculum->EIS ->Semester 5

Curriculum->EIS (Apprenticeship)->Semester 5

Team->

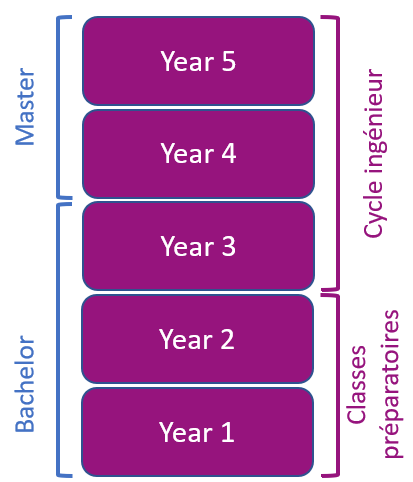

French State controlled diploma conferring a Master's degree

What is a grande école ?

French engineering curriculum