Informations générales

Number of hours

- Lectures 12.0

- Projects -

- Tutorials 6.0

- Internship -

- Laboratory works 9.0

- Written tests -

ECTSECTS

2.5

Goal(s)

At the end of the lecture, the students will be able to design complex digital systems into programmable components (CPLD ou FPGA)

Responsible(s)

Vincent BEROULLE

Content(s)

Lecture chapters

- Introduction

- Programmable components

- Context and issues

- Design flow

- Signal vs. variable

- Why to use programmable components ?

- Design of synchronous digital systems and GALS

- GALS design

- Metastability and signal transmission between clock domains

- Methods for RTL Synthesis

- Synthesis directives issues (ressources sharing, FSM coding...)

- Regular design

- Random design (FSM-based descriptions)

- RTL design : from flow chart to ASMD

- Digital Signal Processing with FPGA

Laboratories

- RTL design application to Xlinx FPGA board (Spartan3E)

Boolean algebra, combinational and sequential logics, binary numbers, MOS transistors, arithmetic operators, Finite State Machine (Moore, Mealy)

Fixed point number representation, digital fourier transform, FIR and IIR digital filters design

Test

- E1 = final written exam (session 1), written, 1h30, only allowed document "Syntaxe VHDL"

- TP = average of laboratory exams

- CC = average of exams done in class or at home

- E2 = final written exam (session 1), written, 1h30, only allowed document "Syntaxe VHDL"

Calendar

The course exists in the following branches:

- Curriculum - EIS - Semester 7

- Curriculum - Network and computer science - Semester 7

Additional Information

Course ID : 4AMCE410

Course language(s):

The course is attached to the following structures:

You can find this course among all other courses.

Bibliography

RTL Hardware design using VHDL, coding for efficiency, portability and scalability, Pong. P. CHU, WILEY INTERSCIENCE

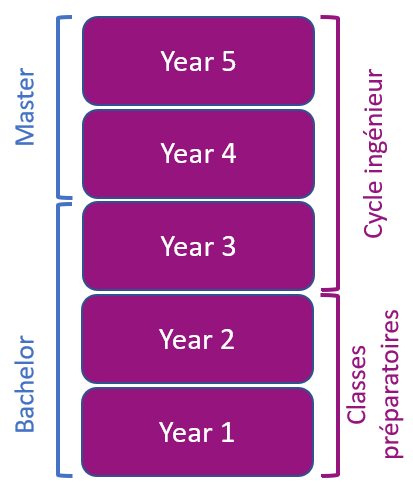

What is a grande école ?

French engineering curriculum