Informations générales

Number of hours

- Lectures 24.0

- Projects -

- Tutorials -

- Internship -

- Laboratory works 18.0

ECTSECTS

0.0

Goal(s)

At the end of the lecture, the students will be able to verify and to test digital secure or critical architectures, and to analyze the robustness of embedded systemes.

General objectives:

*To be able to verify the functionalities of a design

*To be able to test its fabrication

*To be able to analyze the safety and security vulnerabilities of embedded systems

Specific objectives:

*Functional verification techniques

*Testbenches writing, qualification, assertions, emulation, prototyping, formal approaches

for FPGA or ASIC design flows

*Hardware testing

*Fault modeling, test pattern generation, DfT, JTAG

*On-line Printed Circuit Board (PCB) testing

*Robustness and vulnerability analyses

*To be able to choose the most adapted techniques for verification and test

- Advanced techniques for HardWare (HW) and SoftWare (SW) co-design and co-verification:

Virtual Prototyping

**High Level Modelling (TLM, BFM)

**Assertions (PSL)

Responsible(s)

Vincent BEROULLE

Content(s)

*I Introduction

**A Context and Issues

**B Verification vs Test

**C Example of Aeronautical Standard DO-254

*II Hardware Verification

**A Hardware Simulation

***a languages, simulators and levels of abstraction

***b black/white box verifications

***c qualification

***d robustness measurement by fault simulation

***e writing testbench in VHDL (behavioural)

***f assertions (assert, OVL, PSL)

**B Formal verification

***a equivalence checking

***b property/model checking

**C Hardware testing

***a failures and hardware fault models

***b design for test and self test (DfT & BIST)

***c boundary scan

**C Security validation

***a fuzz testing

***b reuse of verification tools

*III Hardware/Software System Co-Verification (HW/SW)

**A Introduction

**B Hardware/Software Partitioning

***a objectives

***b tools (hardware accelerators, high-level synthesis, system design flow)

**C Hardware/software co-development

***a objectives and issues

***b solutions (co-simulation, FPGA prototyping, virtual prototyping)

**D Hardware/Software Co-Verification

***a objectives and solutions

Practical work

Project 1 : VHDL simulation & PSL assertions with QuestaSim (Mentor GraphiCs)

Project 2: Hardware/software co-verification based on virtual prototyping

Mandatory: Hardware Description Language (HDL, verilog or VHDL) for simulation (testbench) and design, logical synthesis, FPGA, processor architecture (processor models, instruction set architecture), C programming

Expected: bases of object oriented programming

Test

E1 = Terminal Exam, First session, written, 2h, only document allowed "syntaxe VHDL", no calculator

TP = average of laboratory exams

E2 = Exam, Second session, written 2h, only document allowed "syntaxe VHDL", no calculator

The exam is given in english only

Calendar

The course exists in the following branches:

- Curriculum - EIS - Semester 9 (this course is given in english only

)

) - Curriculum - EIS (Apprenticeship) - Semester 9 (this course is given in english only

)

) - Curriculum - - Semester 9 (this course is given in english only

)

)

Additional Information

Course ID : 5AMSE517

Course language(s):

The course is attached to the following structures:

You can find this course among all other courses.

Bibliography

- _« Writing testbenches – Functional verification of HDL models », Kluwer, J. Bergeron_

- -« Comprehensive functional verification », B. Wile, Elsevier, 2005_

- -« A practical introduction to PSL », C. Eisner, Springer, 2006_

- -Swarup Bhunia, Sandip Ray, Susmita Sur-Kolay (eds.)-Fundamentals of IP and SoC Security : Design, Verification, and Debug, Springer, 2017_

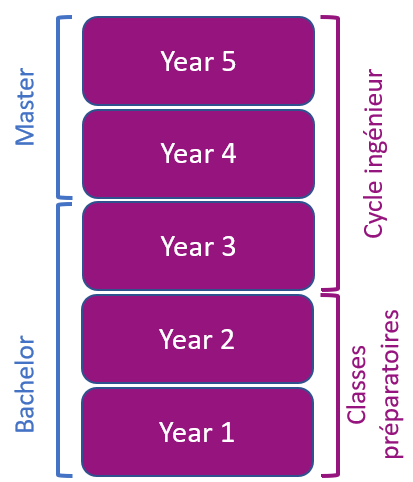

What is a grande école ?

French engineering curriculum